?为什么当寄存器组无限扩大的时候,数据通路会更复杂

不仅仅是因为速度不匹配,同时为了简单数据通路,需要设计 cache

是否可行?

根据 局部性原理 得到是可行的

如何组织?

- 把 cache 划分成相对小的块,访问内存的时候按块存储。使用 cache 的时候如果不命中(缺失处理),则会有额外的装载耗时,称为不命中的惩罚(penalty),这里可以并行优化。

- 程序员操作 cache 的能力只能有 flush ,因为在数据通路上,其他动作都是透明的

- 用有效标识标记是否有效(原则上保证不会出错,顺便可以有 flush 的功能)

映射关系是什么?

有三种方式映射:

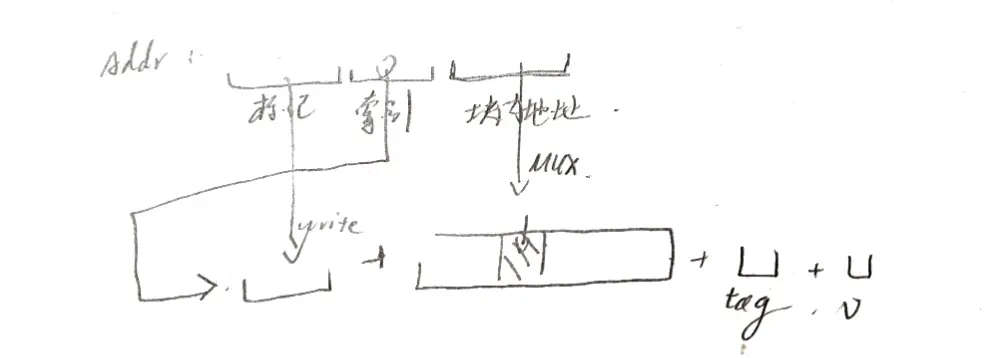

- 直接映射(模映射):每个主存块映射到 cache 的固定行

- 可以直接解读内存地址含义,高位定义为主存标记(标记位)并储存,不一样则没有命中

- 这里局部性就只和块的大小有关

- 全相连:任意映射

- 地址解读为主存标记和块内地址,内存开销较大

- 组相连:每个主存块映射到 Cache 的固定组中的任意一行

- 每一组 N 块称为 N 路组相连

块大小设置成多少?(利用率)cache 地址计算方法?给定一个地址,如何解读?

计算的时候 bit 进位加一成 byte

利用率 = 数据 bits/(有效位 + 标记位 + 数据)

如何更新 cache/淘汰方法?

- FIFO 排队

- 不是一种栈算法,命中率并不会随着组的增大而提高(其实和随机替换没什么区别)

- LRU 最近最少用

- 总是把固定最近一段时间的最少用的那一块淘汰

- 一种实现是:把最近访问的放在队头,把队尾的淘汰,但是在内部这样不好搞。采用计数器,每次命中的时候置零其他加一,淘汰最大的

- LFU

cache 一致性

脏标记:标识这一块已经被改过了

- Write Through (通过式写、写直达、直写)

- 同时写 Cache 和主存单元

- 10% 的存储指令使 CPI 增加到:1.0+100x10%=11

- 使用写缓冲(Write Buffer)

- Write Back (一次性写、写回、回写)

- 只写 cache 不写主存,缺失时一次写回,每行有个修改位(“dirty bit- 脏位”),大大降低主存带宽需求,控制可能很复杂