- 数据通路:在处理器内部进行数据传输和处理的硬件组件的集合,实现数据的运输,计算,移动,存储等等

- 指令周期:CPU 执行完一条指令所需的全部时间

- 操作元件:操作元件是执行指令操作的硬件部件,如 ALU 和寄存器。状态单元用来存储处理器当前的状态,如通用寄存器,PC 等

- 控制单元/执行部件:控制单元负责译码并产生控制信号;执行部件是实际负责完成指令功能的部分

- 拓展器:用于将较小的数据拓展为较大的数据,有符号拓展和逻辑拓展

- 时序信号:控制不同阶段在不同时间顺序执行的信号

- PC/IR/ID:

- PC:指向即将执行的指令地址,每次取地址之后,PC 会自动递增

- IR:用于存储当前正在执行的命令

- ID(指令译码 Instruction Decode):指令周期中对取出的指令进行译码的阶段,确定操作码和操作数

- 微程序控制器:用微程序方式实现的控制器。其基本思想是在时钟控制信号下,仿照程序设计方法,将每一条指令的执行过程用一个微程序来表示,每一个微程序由若干条微指令组成,一个微指令有 n 个微命令,每条微指令相当于有限状态机的一个状态。

- CPU 的基本组成和基本功能

- CPU 由控制单元、算数逻辑单元、寄存器组、数据通路等组成,控制单元负责产生控制信号来控制指令的解读和执行,ALU 负责执行算数运算和逻辑运算,寄存器组用来保存当前状态,数据通路则负责传输数据和指令

- 水平型和垂直型微指令的基本概念和优缺点是什么?

- 水平型微指令:相似的微指令放在一条微指令中,比较复杂

- 垂直型微指令:一条微指令只控制一两个微命令,简单,但是编码要长

- CISC/RISC 微程序设计思路有何不同?

- CISC 指令集较为复杂,每条指令可能需要多条微指令来完成,像 Intel 的流媒体编解码指令,就是一系列复杂的指令合在一起。这样能够减少代码量,并能够存在优化固定算法的空间

- RISC 指令集较为简单,所以通常使用硬布线连接而不是微程序控制器来实现。如果硬要用微程序,其实现也应该是垂直的,即微程序的设计会更加精简(不需要过于复杂),减低学习成本,提升速度

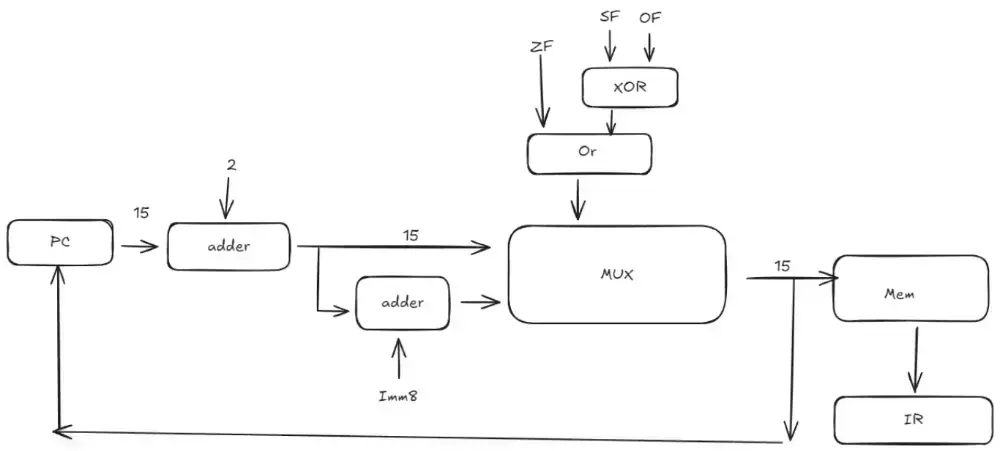

第五章课后作业 4,5,6,7

计算机组成与系统结构(第3版) (袁春风、唐杰、杨若瑜、李俊) (Z-Library) (1), p.179

编址单位是 16 bits,一个指令的长度是 32 bits

- RegWr:所有的 R 型指令,还有 lw 不能写入寄存器组

- Branch:b 的指令不能执行条件满足的时候的跳转,即 PC 永远加 4

- MemWr:sw 不能写入内存

- ExtOp:I 型指令会对负数的识别产生错误,如 lw, sw, addi

- R-type:对 I 型指令利用 ALU 运算会发生 ALU 识别操作错误(用 Imm 的作为 func 了),如 ori, addi, lw, sw

- MemtoReg:在 lw 的时候不能从内存中接受数据

- RegWr:sw 的读内存因为 MemtoReg 的不关心导致结果会未定义,有可能 Rs 中保存的数据向 Rt 或 Rd 中任意一个赋值(取决于 RegDst); beq 也有同样问题;j 就更加复杂,可能会根据 imm 的不同导致寄存器组被任何可能的来源被赋值

- Branch:如果 Zero 恰好为 1,那 PC 会在指令非 j 的时候根据 imm 位置的内容进行偏移跳转

- MemWr:会一直根据输入 ALU 的操作数 B 作为数据,结果作为地址对内存写,对 lw 结果会变成 imm 导入目的寄存器,内存数据也变成 imm;其他的指令只是影响内存中的数据

- ExtOp:I 型指令会对 16 位的无符号整数识别错误,如 addiu, ori

- R-type:对 R 型指令会使得 ALU 无法识别 ALUctr (为 0),可能会有异常产生

- MemtoReg:所有的 R I 型指令返回寄存器的结果是从内存中来的,除了 lw sw(这个不用写如寄存器)之外全部出错,如 add 变为两个寄存器相加结果作为地址,取内存中的数据存在 Sd 中

xor rs, rs, rt # rs = rs ^ rt

xor rt, rs, rt # rt = rs ^ rt (原来的 rs)

xor rs, rs, rt # rs = rs ^ rt (原来的 rt)改动前:

改动后:

如果要改动后占的指令执行时间更短,则占比 x 满足: