名词解释:

- ISA

- instruction set architecture 系统程序员能够感觉到的计算机的功能特性和概念性结构,称为指令集体系结构,简称指令系统

- 操作码

- 指定操作类型的信息

- 地址码

- 操作数或其地址

- GPR/PC/IP/PSW/标志寄存器

- GPR 通用寄存器

- PC 程序计数器

- IP 指令指针

- PSW 程序状态字,包含与处理器状态相关的信息,如中断状态、标志位等,影响程序的执行

- 标志寄存器(EFLAGS),用来存储与运算结果有关的的标志位,如进位标志、溢出标志等

- 寻址方式

- 立即数寻址: 操作数直接作为指令的一部分

- 直接寻址: 操作数的内存地址在指令中指定

- 间接寻址: 指令中给出的是存储操作数地址的地址

- 寄存器直接寻址: 操作数存储在寄存器中,地址码是操作数所在寄存器的编号

- 偏移寻址: 基址和偏移量结合确定操作数地址

- 有效地址

- 指计算出的实际存储地址,且该地址有效。用于访问内存中操作数或数据的最终地址

- CISC/RISC(指令集和 CPU 两方面阐述,举例)

- CISC :复杂指令集,如 x86。包含更多指令,程序代码更短,但是处理器更复杂,处理更慢

- RISC :精简指令集,如 arm,学习成本更低,处理器设计更加简单,功耗更低

- 指令数目少

- 指令格式规整

- 采用 Load/Store 型指令设计风格

- 采用大量通用寄存器

- 采用硬连线控制器

- 采用优化的编译系统

- RISC-V 指令系统

- RISC-V 是一个开源的精简指令集架构,具有模块化设计。它的基本指令集非常小,只有 40 多条指令,适合各种应用场景。RISC-V 指令系统分为基础指令集(如整数计算)和可选扩展(如浮点运算、向量扩展等)。它的设计目标是灵活、高效,并且易于扩展,已在嵌入式系统、移动设备和高性能计算中广泛应用

计算机组成与系统结构(第3版) (袁春风、唐杰、杨若瑜、李俊) (Z-Library) (1), p.142

假设地址为 1200H 的内存单元中的内容为 12FCH, 地址为 12FCH 的内存单元的内容为 38B8H, 而 38B8H 单元的内容为 88F9H。说明以下各情况下操作数的有效地址是多少?

- 操作数采用变址寻址,变址寄存器的内容为 252, 指令中给出的形式地址为 1200H。

1200+FC=12FC

- 操作数采用一次间接寻址,指令中给出的地址码为 1200H。

1200->12FC

- 操作数采用寄存器间接寻址,指令中给出的寄存器编号为 8,8 号寄存器的内容为 1200H。

8->1200->12FC

计算出来的地址都是 12FCH 实际操作数都是 38B8

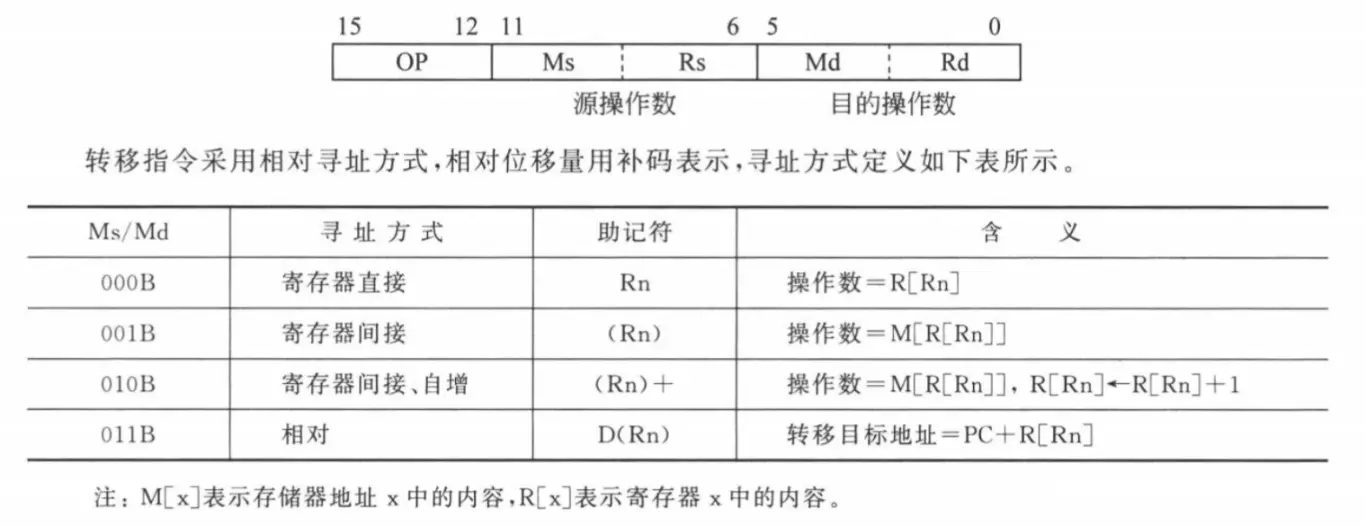

某计算机字长为 16 位,主存地址空间大小为 128KB, 按字编址。采用单字长定长指令格式,指令各字段定义如下:

请回答下列问题:

(1) 该指令系统最多可有多少条指令?最多有多少个通用寄存器?存储器地址寄存器 (MAR) 和存储器数据寄存器 (MDR) 至少各需要多少位?

最多有 个指令,有 8 个通用寄存器,MAR 3 位,MDR 16 位

(2) 转移指令的目标地址范围是多少?

目标地址范围为寄存器表示范围,即 ,相对寻址方式则是能在 范围内转移

(3) 若操作码 0010B 表示加法操作 (助记符为 add), 寄存器 R4 和 R5 的编号分别为 100B 和 101B, R4 的内容为 1234H, R5 的内容为 5678H, 地址 1234H 中的内容为 5678H, 地址 5678H 中的内容为 1234H, 则汇编语句“add (R4), (R5)+”(逗号前为第一源操作数,逗号后为第二源操作数和目的操作数) 对应的机器码是什么 (用十六进制表示)? 该指令执行后,哪些寄存器和存储单元的内容会改变? 改变后的内容是什么?

机器码:

0010 001 100 010 101

R5 内容自增为 5679H,内存中地址 5678H 的内容变为 68AC

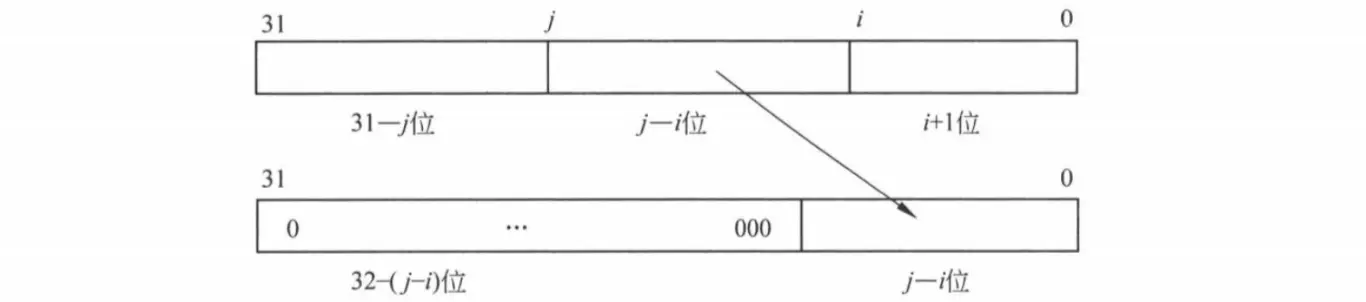

有些计算机提供了专门的指令,能从一个 32 位寄存器中抽取其中任意一个位串置于另一个寄存器的低位有效位上,并在高位补 0, 如下图所示。MIPS 指令系统中没有这样的指令,请写出最短的一个 MIPS 指令序列来实现这个功能,要求 , , 操作前后的寄存器分别为 $s0 和 $s2。

andi $s0,$s0,3FFFFE0H

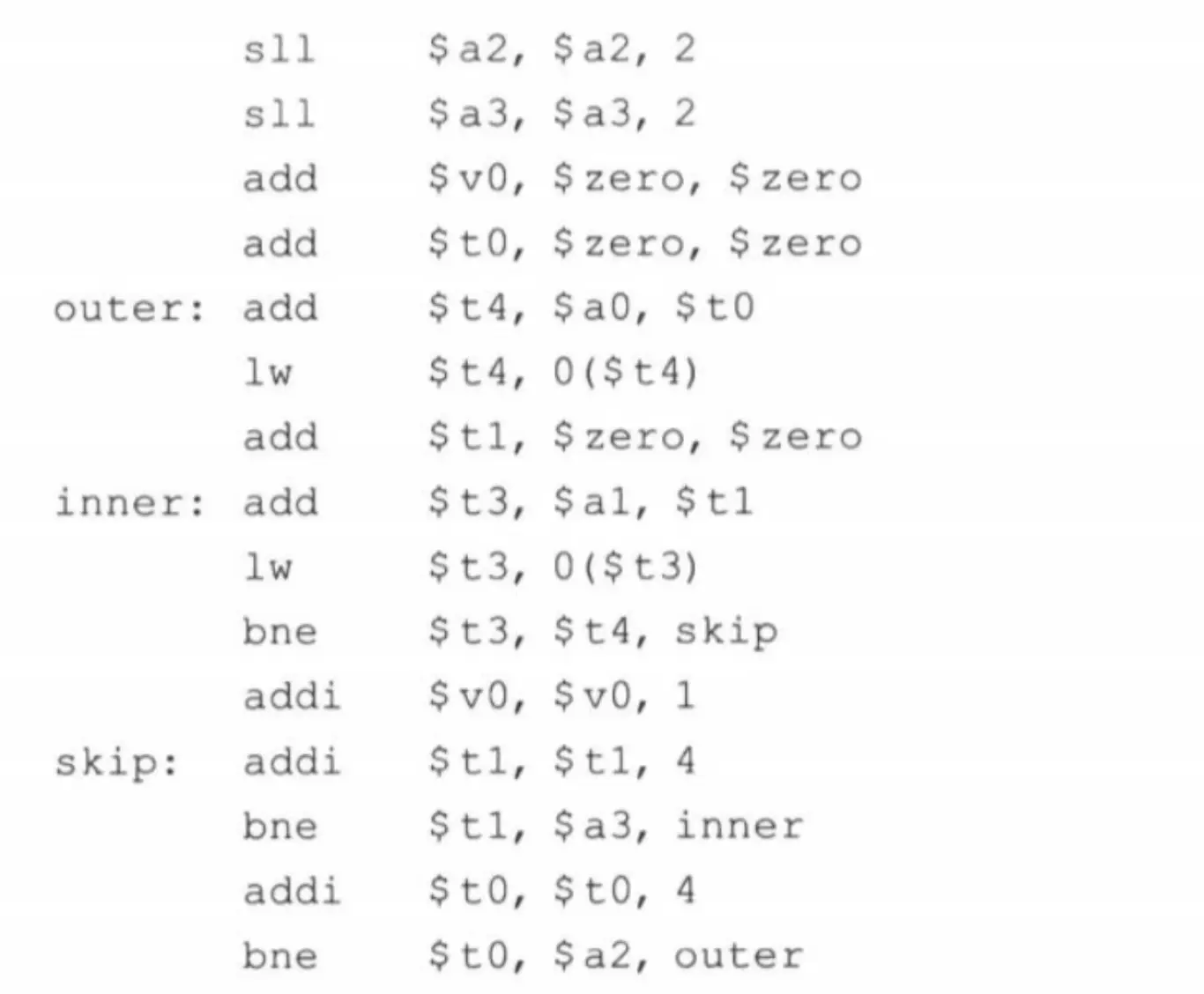

srl $s2,$s0,5下列指令序列用来对两个数组进行处理,并产生结果存放在 $v0 中,两个数组的基地址分别存放在 $aO 和 $a1 中,数组长度分别存放在 $a2 和 $a3 中。要求为以下 MIPS 指令序列加注释,并简单说明该过程的功能。假定每个数组有 2500 个字,其数组下标为 0~2499, 该指令序列运行在一个时钟频率为 2GHz 的处理器上,add、addi 和 sll 指令的 CPI 为 1; lw 和 bne 指令的 CPI 为 2, 则最坏情况下运行所需时间是多少秒?

sll $a2, $a2, 2 # Shift $a2 left by 2 bits (multiplying $a2 by 4)

sll $a3, $a3, 2 # Shift $a3 left by 2 bits (multiplying $a3 by 4)

add $v0, $zero, $zero # Initialize $v0 to 0 (result accumulator)

add $t0, $zero, $zero # Initialize $t0 to 0 (outer loop counter)

outer:

add $t4, $a0, $t0 # Calculate address: base ($a0) + offset ($t0)

lw $t4, 0($t4) # Load word from memory at address in $t4

add $t1, $zero, $zero # Initialize $t1 to 0 (inner loop counter)

inner:

add $t3, $a1, $t1 # Calculate address: base ($a1) + offset ($t1)

lw $t3, 0($t3) # Load word from memory at address in $t3

bne $t3, $t4, skip # Branch to 'skip' if $t3 != $t4

addi $v0, $v0, 1 # Increment $v0 by 1 (count matches)

skip:

addi $t1, $t1, 4 # Increment $t1 by 4 (next element in inner array)

bne $t1, $a3, inner # Repeat inner loop if $t1 != $a3

addi $t0, $t0, 4 # Increment $t0 by 4 (next element in outer array)

bne $t0, $a2, outer # Repeat outer loop if $t0 != $a2该程序的功能是统计这两个数组中相等的数据的对数

最坏情况:

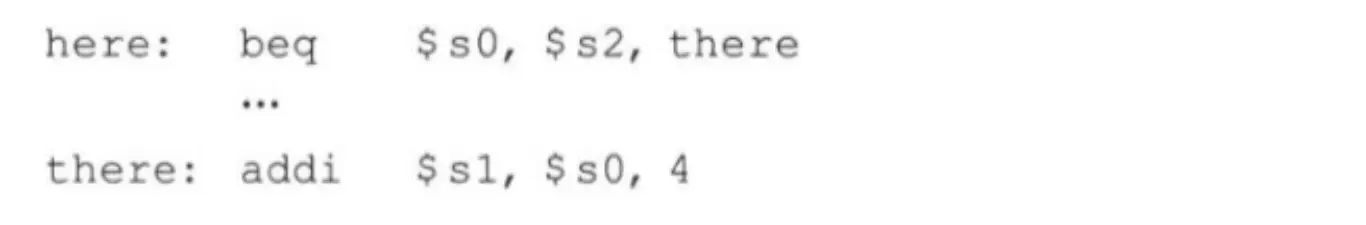

说明 beq 指令的含义,并解释为什么汇编程序在对下列汇编源程序中的 beq 指令进行汇编时会遇到问题,应该如何修改该程序段?

beq :branch equal,当两个操作数相同的时候跳转到对应分支

因为是 R 型指令,所以 there 如果太远的话可能会跳不到对应的地方(所以 branch 最好只在同一个函数内使用)

如果要修改的话可以改成使用两个指令 beq 和 j 配合使用,j 的地址空间更大,可以跳转更多的地方,如果还是不够的话可以用多次 j 中转

here:

bne $s0, $s2, skip

j there

skip:

...

there:

addi $s1, $s0, 4