操作数的流转的路径称为数据通路,通路越多,支持功能越多;通路越短,速度越快

数据通路起始于数据单元的读操作,经过计算单元,结束于数据单元的写操作

理想存储器 对于读操作,应该是组合逻辑单元,不需要时钟信号;写的话就要时钟

用 RTL 寄存器传送语言 将数据通路和指令联系在一起

分散连接方式:所有都连一次

总线连接方式:共享线路,采用 时分复用 的方式;会增加时钟周期,但是时间周期可以做的很快

时钟周期宽度=锁存时延 + 门时延 + 建立时延 + 奇变时间

可以采用三总线的结构减少单总线需要暂存中间变量消耗的时钟,两个源操作数,一个地点操作数

单周期的时钟宽 u 由 sw 决定

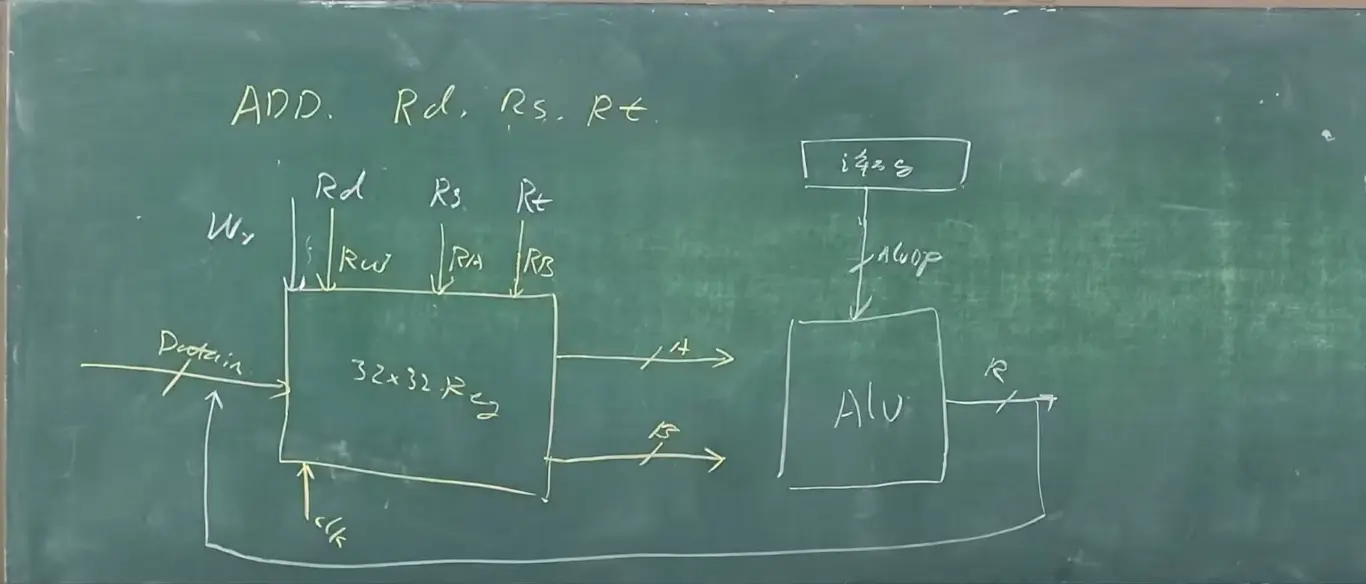

寄存器直接相加型

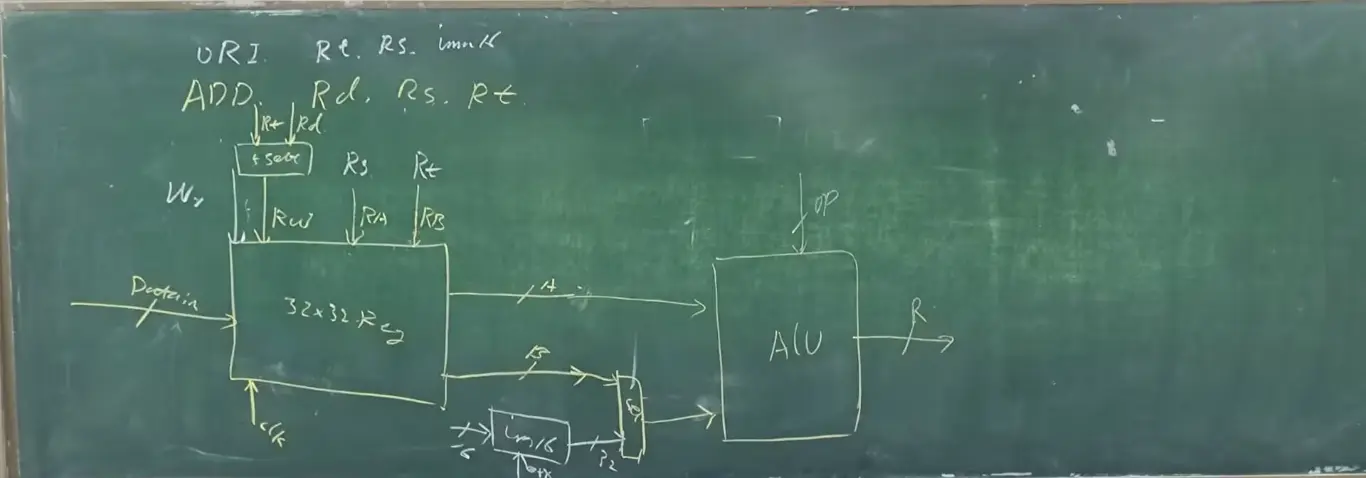

加上立即数(选择器加入)

Rt 此时没用,但是也没有什么影响

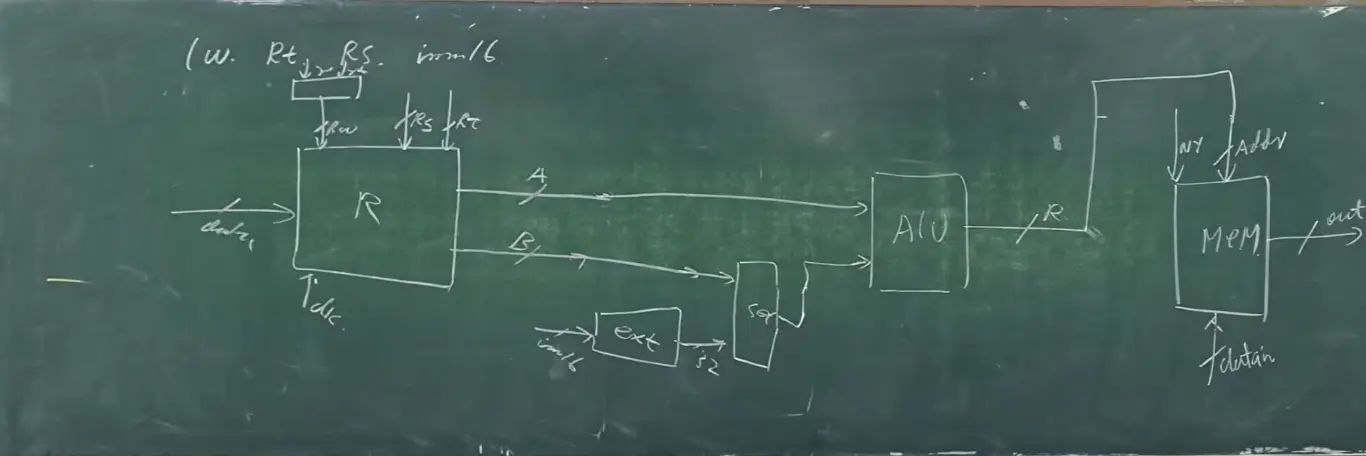

lw 同样这里是理想内存,读操作是组合逻辑,一共 1 级门时延

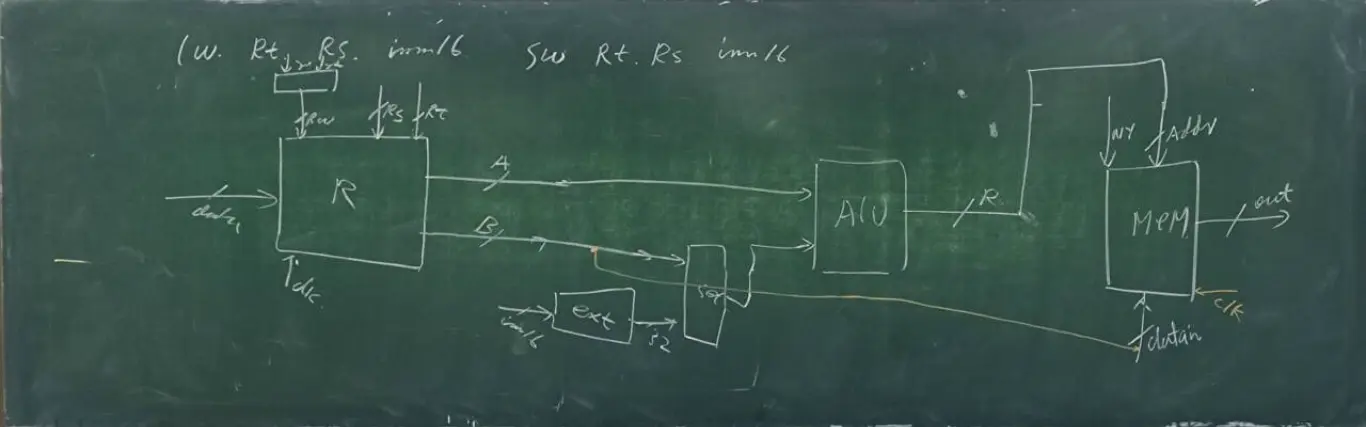

sw 在忽略内存读写差异的情况下通路还更短一点(不用写回去寄存器了),所以以 lw 为最大时钟宽度

通过选择器和使能端控制数据的来源和去向

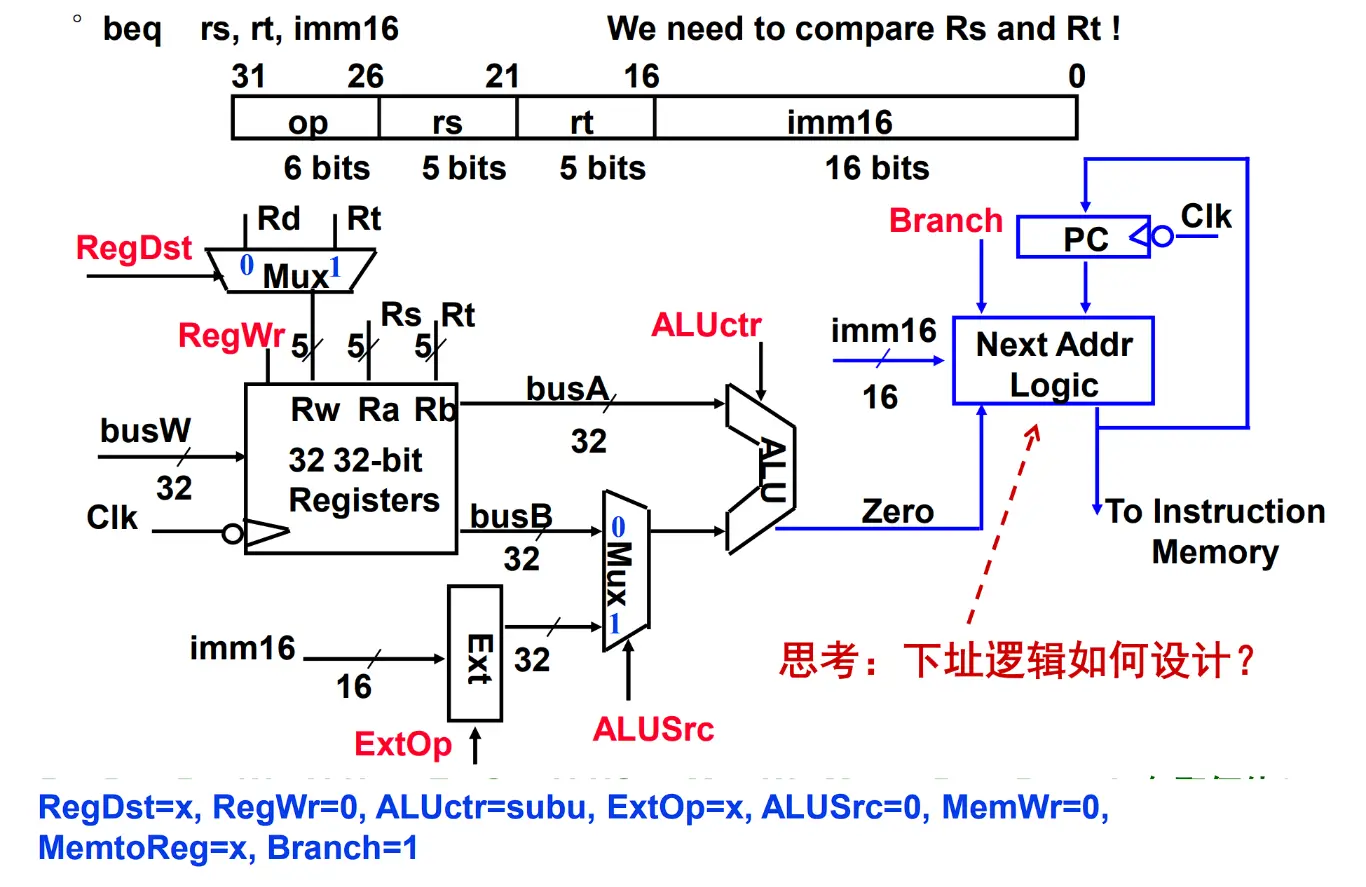

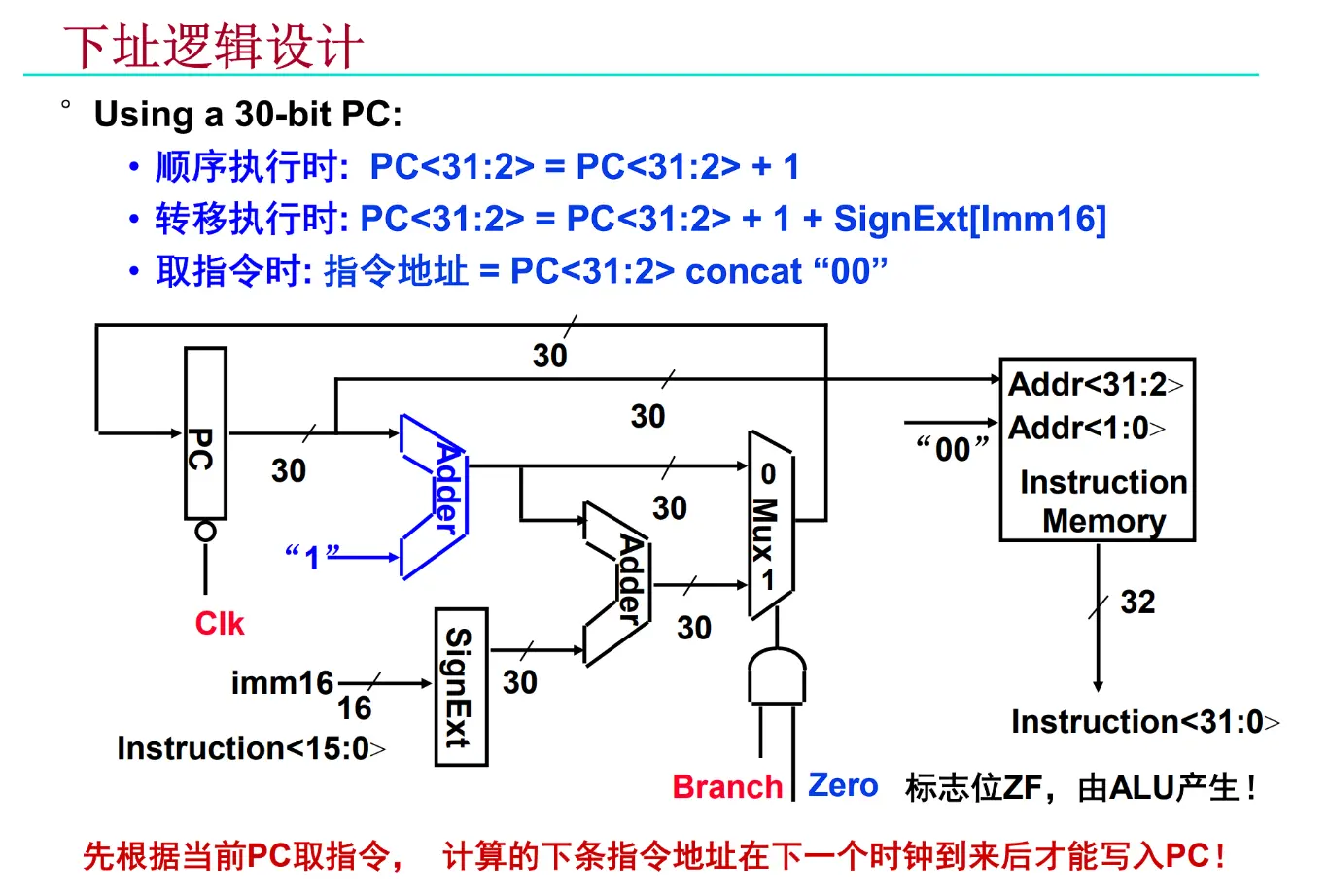

BEQ:

PC <- PC + 4 + 4*imm16

这里修改了 PC 寄存器的内容,后续就没有 PC 自增的操作了

这里基准点取下一条指令 对 jump 0 这条指令就符合逻辑了。同时也有同时性的考量

对于 PC 寄存器检索指令和 ALU 部件是相对独立的部件,可以在某些操作上并行执行

j 计算机底层就对跳转的地方做出限制了